## 8755A/8755A-2 16,384-BIT EPROM WITH I/O

- 2048 Words × 8 Bits

- Single +5V Power Supply (V<sub>cc</sub>)

- Directly Compatible with 8085A and 8088 Microprocessors

- U.V. Erasable and Electrically Reprogrammable

- Internal Address Latch

- 2 General Purpose 8-Bit I/O Ports

- Each I/O Port Line Individually Programmable as Input or Output

- Multiplexed Address and Data Bus

- 40-Pin DIP

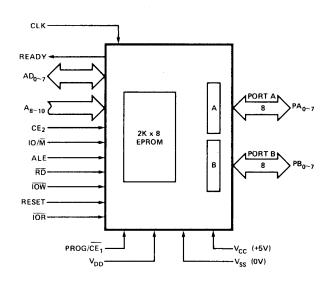

The Intel® 8755A is an erasable and electrically reprogrammable ROM (EPROM) and I/O chip to be used in the 8085A and 8088 microprocessor systems. The EPROM portion is organized as 2048 words by 8 bits. It has a maximum access time of 450 ns to permit use with no wait states in an 8085A CPU.

The I/O portion consists of 2 general purpose I/O ports. Each I/O port has 8 port lines, and each I/O port line is individually programmable as input or output.

The 8755A-2 is a high speed selected version of the 8755A compatible with the 5 MHz 8085A-2 and the full speed 5 MHz 8088.

#### PIN CONFIGURATION

#### PROG AND CE1 □ V<sub>CC</sub> CE<sub>2</sub> □ PB<sub>7</sub> CLK [ PB<sub>6</sub> 38 RESET [ \_ PB<sub>5</sub> □ РВ<sub>4</sub> ∿DD [ 36 PB<sub>3</sub> READY [ 35 ю/й □ 34 PB<sub>2</sub> 33 PB<sub>1</sub> IOR [ □ PB<sub>0</sub> RD 🗆 32 □PA<sub>7</sub> **iow** □ 10 8755A/ 31 ALE 11 8755A-2 30 PA<sub>6</sub> AD<sub>0</sub> | 12 29 PA<sub>5</sub> AD<sub>1</sub> 🔲 13 28 PA<sub>4</sub> PA<sub>3</sub> AD<sub>2</sub> 14 27 AD<sub>3</sub> 15 26 □PA<sub>2</sub> AD<sub>4</sub> 🗖 16 PA<sub>1</sub> 25 AD<sub>5</sub> [ 17 24 PA<sub>0</sub> AD<sub>6</sub> ☐ 18 23 A 10 AD<sub>7</sub> □ A<sub>9</sub> 19 22 V<sub>ss</sub> □ 20

#### **BLOCK DIAGRAM**

#### 8755A FUNCTIONAL PIN DEFINITION

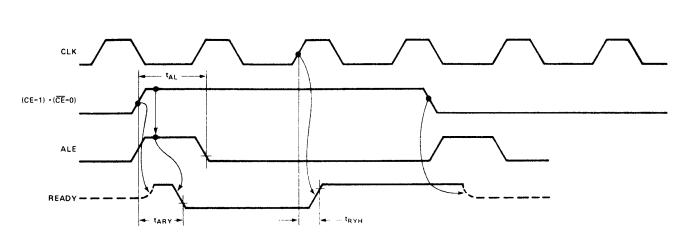

| Symbol<br>ALE<br>(input)                           | Function  When Address Latch Enable goes high, AD <sub>0-7</sub> , IO/M, A <sub>8-10</sub> , CE <sub>2</sub> , and CE <sub>1</sub> enter the address latches. The signals (AD, IO/M, A <sub>8-10</sub> , CE) are latched in at the trailing edge of ALE.                                                                       | Symbol<br>READY<br>(output)         | Function  READY is a 3-state output controlled by CE <sub>2</sub> , CE <sub>1</sub> , ALE and CLK. READY is forced low when the Chip Enables are active during the time ALE is high, and remains low until the rising edge of the next CLK. (See Figure 6.)                                    |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD <sub>0</sub> -7<br>(input/output)               | Bidirectional Address/Data bus. The lower 8-bits of the PROM or I/O address are applied to the bus lines when ALE is high.  During an I/O cycle, Port A or B are selected based on the latched value of AD <sub>0</sub> . If RD or IOR is low when the latched Chip Enables are active, the output buffers present data on the | PA <sub>0-7</sub><br>(input/output) | These are general purpose I/O pins. Their input/output direction is determined by the contents of Data Direction Register (DDR). Port Aisselected for write operations when the Chip Enables are active and IOW is low and a 0 was previously latched from AD <sub>0</sub> , AD <sub>1</sub> . |

| A8-10<br>(input)                                   | bus. These are the high order bits of the PROM address. They do not affect I/O operations.                                                                                                                                                                                                                                     |                                     | Read operation is selected by either IOR low and active Chip Enables and AD <sub>0</sub> and AD <sub>1</sub> low, or IO/M high, RD low, active Chip Enables, and AD <sub>0</sub> and AD <sub>1</sub> low.                                                                                      |

| PROG/CE <sub>1</sub><br>CE <sub>2</sub><br>(input) | Chip Enable Inputs: CE <sub>1</sub> is active low and CE <sub>2</sub> is active high. The 8755A can be accessed only when BOTH Chip Enables are active at the time the ALE signal latches them up. If                                                                                                                          | PB <sub>0-7</sub><br>(input/output) | This general purpose I/O port is identical to Port A except that it is selected by a 1 latched from $AD_0$ and a 0 from $AD_1$ .                                                                                                                                                               |

|                                                    | either Chip Enable input is not active,<br>the AD <sub>0-7</sub> and READY outputs will<br>be in a high impedance state. CE <sub>1</sub> is<br>also used as a programming pin. (See<br>section on programming.)                                                                                                                | RESET (input)                       | In normal operation, an input high on RESET causes all pins in Ports A and B to assume input mode (clear DDR register).                                                                                                                                                                        |

| IO/M<br>(input)                                    | If the latched IO/M is high when RD is low, the output data comes from an I/O port. If it is low the output data comes from the PROM.                                                                                                                                                                                          | IOR<br>(input)                      | When the Chip Enables are active, a low on IOR will output the selected I/O port onto the AD bus. IOR low performs the same function as the combination of IO/M high and RD                                                                                                                    |

| RD<br>(input)                                      | If the latched Chip Enables are active when $\overline{RD}$ goes low, the $AD_{0-7}$ output                                                                                                                                                                                                                                    |                                     | low. When IOR is not used in a system, IOR should be tied to V <sub>CC</sub> ("1").                                                                                                                                                                                                            |

|                                                    | buffers are enabled and output either the selected PROM location or I/O                                                                                                                                                                                                                                                        | V <sub>CC</sub><br>V <sub>SS</sub>  | +5 volt supply.  Ground Reference.                                                                                                                                                                                                                                                             |

|                                                    | port. When both RD and IOR are high, the AD <sub>0-7</sub> output buffers are 3-stated.                                                                                                                                                                                                                                        | V <sub>DD</sub>                     | V <sub>DD</sub> is a programming voltage, and                                                                                                                                                                                                                                                  |

| <del>IOW</del>                                     | If the latched Chip Enables are active,                                                                                                                                                                                                                                                                                        |                                     | must be tied to +5V when the 8755A is being read.                                                                                                                                                                                                                                              |

| (input)                                            | a low on IOW causes the output port pointed to by the latched value of $AD_0$ to be written with the data on $AD_{0-7}$ . The state of $IO/\overline{M}$ is ignored.                                                                                                                                                           |                                     | For programming, a high voltage is supplied with $V_{DD} = 25V$ , typical. (See section on programming.)                                                                                                                                                                                       |

| CLK<br>(input)                                     | The CLK is used to force the READY into its high impedance state after it has been forced low by CE <sub>1</sub> low, CE <sub>2</sub> high, and ALE high.                                                                                                                                                                      |                                     |                                                                                                                                                                                                                                                                                                |

# FUNCTIONAL DESCRIPTION PROM Section

The 8755A contains an 8-bit address latch which allows it to interface directly to MCS-48 and MCS-85 Microcomputers without additional hardware.

The PROM section of the chip is addressed by the 11-bit address and CE. The address,  $\overline{CE}_1$  and  $CE_2$  are latched into the address latches on the falling edge of ALE. If the latched Chip Enables are active and  $IO/\overline{M}$  is low when  $\overline{RD}$  goes low, the contents of the PROM location addressed by the latched address are put out on the  $AD_{0-7}$  lines.

#### I/O Section

The I/O section of the chip is addressed by the latched value of  $AD_{0-1}$ . Two 8-bit Data Direction Registers (DDR) in 8755A determine the input/output status of each pin in the corresponding ports. A "0" in a particular bit position of a DDR signifies that the corresponding I/O port bit is in the input mode. A "1" in a particular bit position signifies that the corresponding I/O port bit is in the output mode. In this manner the I/O ports of the 8755A are bit-by-bit programmable as inputs or outputs. The table summarizes port and DDR designation. DDR's cannot be read.

| AD <sub>1</sub> | AD <sub>0</sub> | Selection                              |

|-----------------|-----------------|----------------------------------------|

| 0               | 0               | Port A                                 |

| 0               | 1               | Port B                                 |

| 1               | 0               | Port A Data Direction Register (DDR A) |

| 1               | 1               | Port B Data Direction Register (DDR B) |

When IOW goes low and the Chip Enables are active, the data on the AD is written into I/O port selected by the latched value of AD<sub>0-1</sub>. During this operation all I/O bits of the selected port are affected, regardless of their I/O mode and the state of IO/ $\overline{\rm M}$ . The actual output level does not change until  $\overline{\rm IOW}$  returns high. (glitch free output)

A port can be read out when the latched Chip Enables are active and either RD goes low with IO/M high, or IOR goes low. Both input and output mode bits of a selected port will appear on lines  $AD_{0-7}$ .

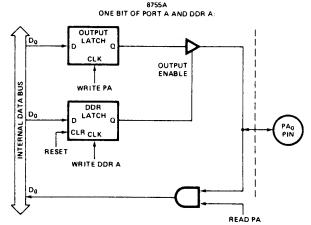

To clarify the function of the I/O Ports and Data Direction Registers, the following diagram shows the configuration of one bit of PORT A and DDR A. The same logic applies to PORT B and DDR B.

WRITE PA =  $(\overline{IOW}=0)$  + (CHIP ENABLES ACTIVE) • (PORT A ADDRESS SELECTED)

WRITE DOR A =  $(\overline{IOW}=0)$  • (CHIP ENABLES ACTIVE) • (IODR A ADDRESS SELECTED)

READ PA =  $\{(\overline{IOM}=1)$  •  $(\overline{IOR}=0)$  •  $(\overline{IOR}=0)$  • (CHIP ENABLES ACTIVE) • (PORT A ADDRESS SELECTED)

NOTE: WRITE PA IS NOT QUALIFIED BY  $|\overline{IOM}|$ .

Note that hardware RESET or writing a zero to the DDR latch will cause the output latch's output buffer to be disabled, preventing the data in the Output Latch from being passed through to the pin. This is equivalent to putting the port in the input mode. Note also that the data can be written to the Output Latch even though the Output Buffer has been disabled. This enables a port to be initialized with a value prior to enabling the output.

The diagram also shows that the contents of PORT A and PORT B can be read even when the ports are configured as outputs.

TABLE 1. 8755A PROGRAMMING MODULE CROSS REFERENCE

| MOD                   | DULE NAME                                                  | USE WITH                                             |

|-----------------------|------------------------------------------------------------|------------------------------------------------------|

| PRO                   | 955<br>UP2(2)<br>MPT 975<br>MPT 475                        | UPP(4)<br>UPP 855<br>PROMPT 80/85(3)<br>PROMPT 48(1) |

| NOT<br>1.<br>2.<br>3. | ES: Described on p. 1 Special adaptor so Described on p. 1 | 3-34 of 1978 Data Catalog.                           |

#### **ERASURE CHARACTERISTICS**

The erasure characteristics of the 8755A are such that erasure begins to occur when exposed to light with wavelengths shorter than approximately 4000 Angstroms (Å). It should be noted that sunlight and certain types of fluorescent lamps have wavelengths in the 3000-4000Å range. Data show that constant exposure to room level fluorescent lighting could erase the typical 8755A in approximately 3 years while it would take approximately 1 week to cause erasure when exposed to direct sunlight. If the 8755A is to be exposed to these types of lighting conditions for extended periods of time, opaque labels are available from Intel which should be placed over the 8755 window to prevent unintentional erasure.

The recommended erasure procedure for the 8755A is exposure to shortwave ultraviolet light which has a wavelength of 2537 Angstroms (Å). The integrated dose (i.e., UV intensity X exposure time) for erasure should be a minimum of 15W-sec/cm². The erasure time with this dosage is approximately 15 to 20 minutes using an ultraviolet lamp with a  $12000\mu \text{W/cm}^2$  power rating. The 8755A should be placed within one inch from the lamp tubes during erasure. Some lamps have a filter on their tubes and this filter should be removed before erasure.

#### **PROGRAMMING**

Initially, and after each erasure, all bits of the EPROM portions of the 8755A are in the "1" state. Information is introduced by selectively programming "0" into the desired bit locations. A programmed "0" can only be changed to a "1" by UV erasure.

The 8755A can be programmed on the Intel® Universal PROM Programmer (UPP), and the PROMPT™ 80/85 and PROMPT-48™ design aids. The appropriate programming modules and adapters for use in programming both 8755A's and 8755's are shown in Table 1.

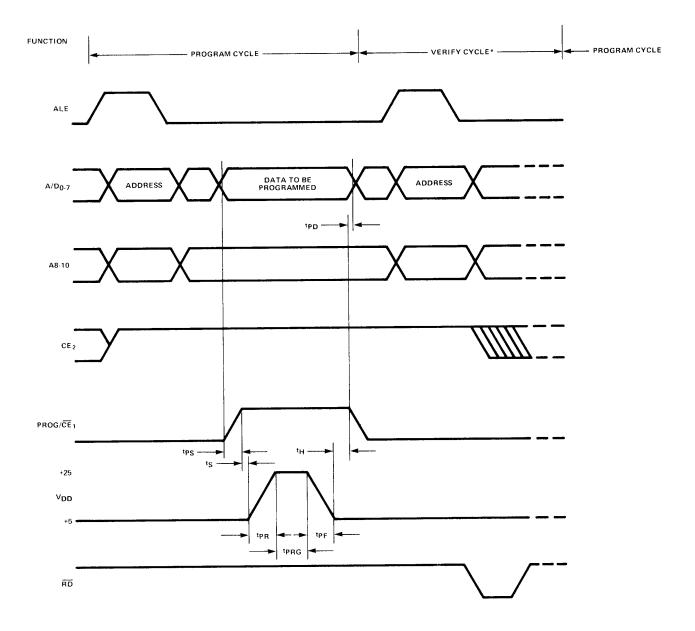

The program mode itself consists of programming a single address at a time, giving a single 50 msec pulse for every address. Generally, it is desirable to have a verify cycle after a program cycle for the same address as shown in the attached timing diagram. In the verify cycle (i.e., normal memory read cycle) 'Vpp' should be at +5V.

Preliminary timing diagrams and parameter values pertaining to the 8755A programming operation are contained in Figure 7.

#### SYSTEM APPLICATIONS

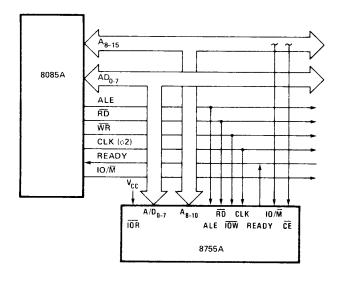

#### System Interface with 8085A and 8088

A system using the 8755A can use either one of the two I/O Interface techniques:

- Standard I/O

- Memory Mapped I/O

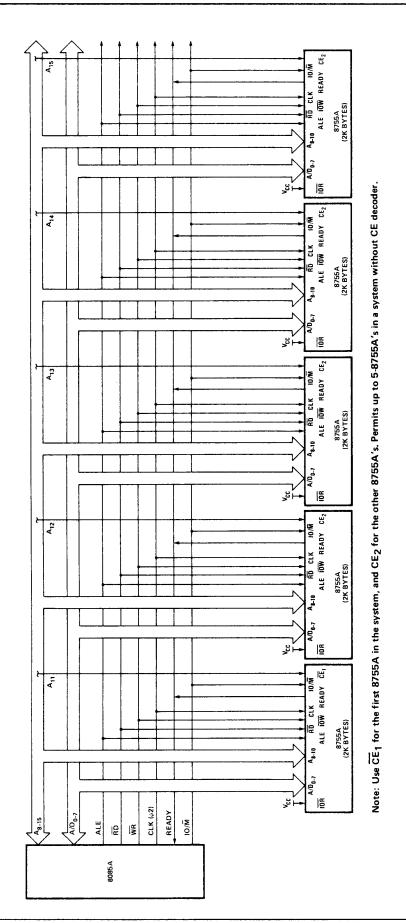

If a standard I/O technique is used, the system can use the feature of both CE $_3$  and CE $_1$ . By using a combination of unused address lines  $A_{11-15}$  and the Chip Enable inputs, the 8085A system can use up to 5 each 8755A's without requiring a CE decoder. See Figure 2a and 2b.

If a memory mapped I/O approach is used the 8755A will be selected by the combination of both the Chip Enables and  $IO/\overline{M}$  using the AD<sub>8-15</sub> address lines. See Figure 1.

Figure 1. 8755A in 8085A System(Memory-Mapped I/O)

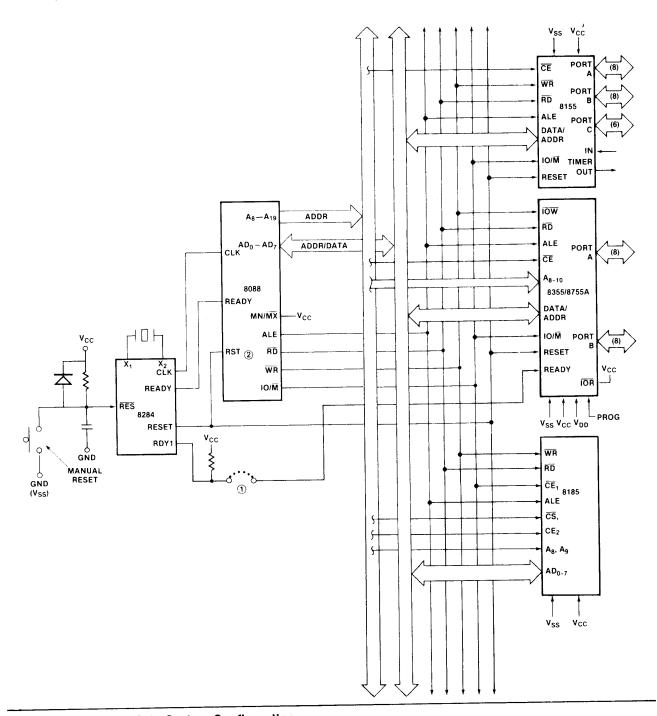

#### 8088 FIVE CHIP SYSTEM

Figure 1b shows a five chip system containing:

- 1.25 K Bytes RAM

- 2 K Bytes ROM

- 38 I/O Pins

- 1 Interval Timer

- 2 Interrupt Levels

Figure 2a. 8088 Five Chip System Configuration

Figure 2b. 8755A in 8085A System (Standard I/O)

### **ABSOLUTE MAXIMUM RATINGS\***

| Temperature Under Bias 0°C to +70°C |

|-------------------------------------|

| Storage Temperature65°C to +150°C   |

| Voltage on Any Pin                  |

| With Respect to Ground0.5V to +7V   |

| Power Dissipation 1.5W              |

"COMMENT: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **D.C. CHARACTERISTICS** $(T_A = 0^{\circ}C \text{ to } 70^{\circ}C; V_{CC} = 5V \pm 5\%)$

| SYMBOL           | PARAMETER                      | MIN. | MAX.                 | UNITS | TEST CONDITIONS                          |

|------------------|--------------------------------|------|----------------------|-------|------------------------------------------|

| V <sub>IL.</sub> | Input Low Voltage              | -0.5 | 0.8                  | V     | V <sub>CC</sub> = 5.0V                   |

| ViH              | Input High Voltage             | 2.0  | V <sub>CC</sub> +0.5 | V     | V <sub>CC</sub> = 5.0V                   |

| Vol              | Output Low Voltage             |      | 0.45                 | V     | I <sub>OL</sub> = 2mA                    |

| Voн              | Output High Voltage            | 2.4  |                      | V     | I <sub>OH</sub> = -400μA                 |

| կլ               | Input Leakage                  |      | 10                   | μΑ    | $V_{IN} = V_{CC}$ to $0V$                |

| I <sub>LO</sub>  | Output Leakage Current         |      | ±10                  | μΑ    | 0.45V ≤V <sub>OUT</sub> ≤V <sub>CC</sub> |

| lcc              | V <sub>CC</sub> Supply Current |      | 180                  | mA    |                                          |

## **A.C. CHARACTERISTICS** $(T_A = 0^{\circ}C \text{ to } 70^{\circ}C; V_{CC} = 5V \pm 5\%)$

|                                | Parameter                              | 8755A |      | 8755A-2<br>(Preliminary) |      |       |

|--------------------------------|----------------------------------------|-------|------|--------------------------|------|-------|

| Symbol                         |                                        | Min.  | Max. | Min.                     | Max. | Units |

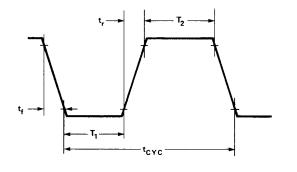

| tcyc                           | Clock Cycle Time                       | 320   |      | 200                      |      | ns    |

| T <sub>1</sub>                 | CLK Pulse Width                        | 80    |      | 40                       |      | ns    |

| T <sub>2</sub>                 | CLK Pulse Width                        | 120   |      | 70                       |      | ns    |

| t <sub>f</sub> ,t <sub>r</sub> | CLK Rise and Fall Time                 |       | 30   |                          | 30   | ns    |

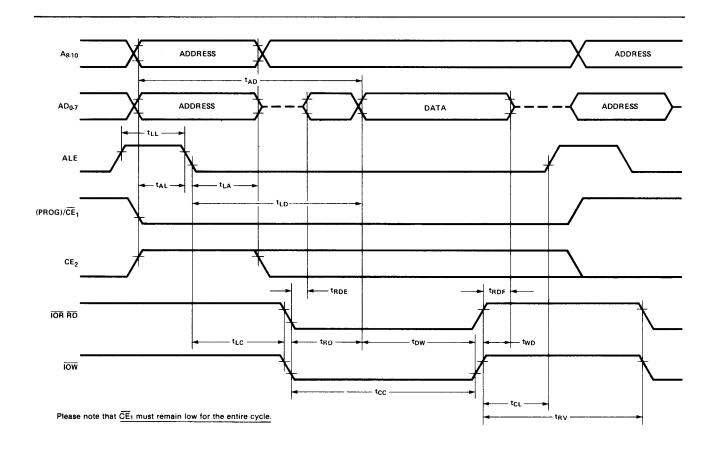

| tal                            | Address to Latch Set Up Time           | 50    |      | 30                       |      | ns    |

| t <sub>LA</sub>                | Address Hold Time after Latch          | 80    |      | 45                       |      | ns    |

| tLC                            | Latch to READ/WRITE Control            | 100   |      | 40                       |      | ns    |

| tRD                            | Valid Data Out Delay from READ Control |       | 170  |                          | 140  | ns    |

| tab                            | Address Stable to Data Out Valid       |       | 450  |                          | 330  | ns    |

| tLL                            | Latch Enable Width                     | 100   |      | 70                       |      | ns    |

| trdf                           | Data Bus Float after READ              | 0     | 100  | 0                        | 85   | ns    |

| toL                            | READ/WRITE Control to Latch Enable     | 20    |      | 10                       |      | ns    |

| toc                            | READ/WRITE Control Width               | 250   |      | 200                      |      | ns    |

| t <sub>DW</sub>                | Data In to Write Set Up Time           | 150   |      | 150                      |      | ns    |

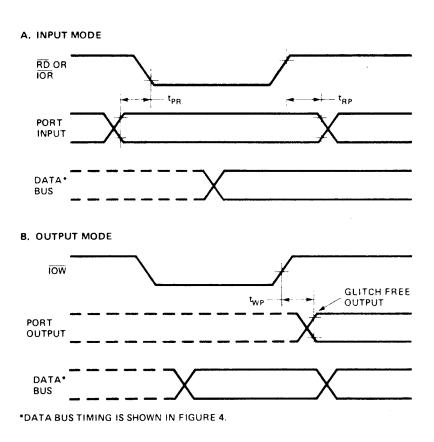

| twp                            | Data In Hold Time After WRITE          | 30    |      | 10                       |      | ns    |

| twp                            | WRITE to Port Output                   |       | 400  |                          | 400  | ns    |

| tpR                            | Port Input Set Up Time                 | 50    |      | 50                       |      | ns    |

| t <sub>RP</sub>                | Port Input Hold Time                   | 50    |      | 50                       |      | ns    |

| tryh                           | READY HOLD Time                        | 0     | 160  | 0                        | 160  | ns    |

| tary                           | ADDRESS (CE) to READY                  |       | 160  |                          | 160  | ns    |

| t <sub>RV</sub>                | Recovery Time Between Controls         | 300   |      | 200                      |      | ns    |

| tRDE                           | READ Control to Data Bus Enable        | 10    |      | 10                       |      | ns    |

| t <sub>LD</sub>                | ALE to Data Out Valid                  |       | 350  |                          | 270  | ns    |

Note: CLOAD = 150pF

#### Input Waveform for A.C. Tests:

#### **WAVEFORMS**

Figure 3. Clock Specification for 8755A

Figure 4. PROM Read, I/O Read and Write Timing

Figure 5. I/O Port Timing

Figure 6. Wait State Timing (READY = 0)

#### D.C. SPECIFICATION PROGRAMMING

$(T_A = 0^{\circ}C \text{ to } 70^{\circ}C; V_{CC} = 5V \pm 5\%; V_{SS} = 0V)$

| Symbol          | Parameter                                   | Min. | Тур. | Max. | Unit |

|-----------------|---------------------------------------------|------|------|------|------|

| V <sub>DD</sub> | Programming Voltage (during Write to EPROM) | 24   | 25   | 26   | V    |

| IDD             | Prog Supply Current                         |      | 15   | 30   | mA   |

#### A.C. SPECIFICATION FOR PROGRAMMING

$(T_A = 0^{\circ}C \text{ to } 70^{\circ}C; V_{CC} = 5V \pm 5\%; V_{SS} = 0V)$

| Symbol | Parameter             | Min. | Тур. | Max. | Unit |

|--------|-----------------------|------|------|------|------|

| tps    | Data Setup Time       | 10   |      |      | ns   |

| tpD    | Data Hold Time        | 0    |      |      | ns   |

| ts     | Prog Pulse Setup Time | 2    |      |      | μS   |

| tн     | Prog Pulse Hold Time  | 2    |      |      | μS   |

| tpR    | Prog Pulse Rise Time  | 0.01 | 2    |      | μS   |

| tpf    | Prog Pulse Fall Time  | 0.01 | 2    |      | μS   |

| tprg   | Prog Pulse Width      | 45   | 50   |      | msec |

#### **WAVEFORMS**

\*VERIFY CYCLE IS A REGULAR MEMORY READ CYCLE (WITH  $V_{\mbox{DD}}$  = +5V FOR 8755A)

Figure 7. 8755A Program Mode Timing Diagram