# 8205 HIGH SPEED 1 OUT OF 8 BINARY DECODER

- I/O Port or Memory Selector

- Simple Expansion Enable Inputs

- High Speed Schottky Bipolar Technology — 18ns Max. Delay

- Directly Compatible with TTL Logic Circuits

- Low Input Load Current .25 mA max., 1/6 Standard TTL Input Load

- Minimum Line Reflection Low Voltage Diode Input Clamp

- Outputs Sink 10 mA min.

- 16-Pin Dual-In-Line Ceramic or Plastic Package

The Intel® 8205 decoder can be used for expansion of systems which utilize input ports, output ports, and memory components with active low chip select input. When the 8205 is enabled, one of its 8 outputs goes "low," thus a single row of a memory system is selected. The 3-chip enable inputs on the 8205 allow easy system expansion. For very large systems, 8205 decoders can be cascaded such that each decoder can drive 8 other decoders for arbitrary memory expansions.

The 8205 is packaged in a standard 16-pin dual in-line package, and its performance is specified over the temperature range of 0°C to +75°C, ambient. The use of Schottky barrier diode clamped transistors to obtain fast switching speeds results in higher performance than equivalent devices made with a gold diffussion process.

| ADDRESS        |    | E٨             | JABL | .€  |     |   | ( | OUTP | UTS |   |   |    |   |

|----------------|----|----------------|------|-----|-----|---|---|------|-----|---|---|----|---|

| A <sub>0</sub> | Αı | A <sub>2</sub> | Εı   | E 2 | E 3 | ٥ | 1 | 2    | 3   | 4 | 5 | 6  | 7 |

| L              | L  | τ              | L    | L   | н   | ٦ | н | н    | н   | н | н | н  | н |

| н              | L  | L              | L    | L   | н   | н | Ł | н    | н   | н | Н | н  | н |

| Ļ              | н  | L              | L    | L   | н   | н | н | L    | н   | н | н | н  | н |

| н              | н  | L.             | L    | L.  | н   | н | н | н    | L   | н | н | н  | н |

| L              | L  | н              | L    | L   | н   | H | н | н    | н   | L | н | 14 | н |

| Ή.             | L  | н              | L    | L   | н   | н | н | н    | н   | н | L | н  | н |

| L              | н  | н              | L    | L   | н   | н | н | н    | н   | н | н | L  | н |

| н              | H  | н              | L    | L   | н.  | н | н | н    | н   | н | н | H  | L |

| х              | х  | х              | L    | L   | L   | H | H | н    | н   | H | н | н  | н |

| X              | х  | X              | н    | L   | L   | н | н | н    | н   | н | н | н  | н |

| X              | ×  | x              | L    | н   | L   | н | н | н    | н   | н | н | н  | н |

| х              | х  | X              | H    | н   | L   | H | н | н    | н   | н | н | H  | н |

| X              | х  | х              | н    | L   | н   | н | н | н    | н   | н | н | н  | н |

| х              | X  | х              | L    | н   | н   | н | н | н    | н   | н | H | н  | н |

| х              | х  | x              | н    | н   | н   | н | н | н    | н   | H | н | н  | н |

|   | A <sub>0</sub> - A <sub>2</sub> | ADDRESS INPUTS  |

|---|---------------------------------|-----------------|

|   | Ē₁·Ē₃                           | ENABLE INPUTS   |

| j | 00 07                           | DECODED OUTPUTS |

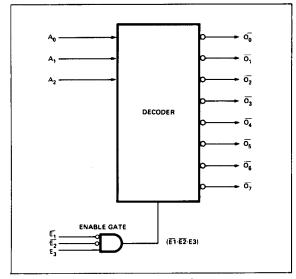

Figure 1. Logic Symbol

Figure 2. Pin Configuration

#### **FUNCTIONAL DESCRIPTION**

#### Decoder

The 8205 contains a one out of eight binary decoder. It accepts a three bit binary code and by gating this input, creates an exclusive output that represents the value of the input code.

For example, if a binary code of 101 was present on the A0, A1 and A2 address input lines, and the device was enabled, an active low signal would appear on the  $\overline{05}$  output line. Note that all of the other output pins are sitting at a logic high, thus the decoded output is said to be exclusive. The decoders outputs will follow the truth table shown below in the same manner for all other input variations.

#### **Enable Gate**

When using a decoder it is often necessary to gate the outputs with timing or enabling signals so that the exclusive output of the decoded value is synchronous with the overall system.

The 8205 has a built-in function for such gating. The three enable inputs ( $\overline{E1}$ ,  $\overline{E2}$ ,  $\overline{E3}$ ) are ANDed together and create a single enable signal for the decoder. The combination of both active "high" and active "low" device enable inputs provides the designer with a powerfully flexible gating function to help reduce package count in his system.

Figure 3. Enable Gate

| ADDRESS        |                |                | E١             | IABL           | Æ              | OUTPUTS |   |   |   |   |   |   |   |

|----------------|----------------|----------------|----------------|----------------|----------------|---------|---|---|---|---|---|---|---|

| A <sub>0</sub> | A <sub>1</sub> | A <sub>2</sub> | E <sub>1</sub> | E <sub>2</sub> | E <sub>3</sub> | 0       | 1 | 2 | 3 | 4 | 5 | G | 7 |

| L              | L              | L              | L              | L              | I              | L       | Н | Н | Н | Н | н | Н | Н |

| н              | Ł              | L              | L              | L              | н              | н       | L | н | н | н | н | н | н |

| L              | Н              | L              | L              | L              | н              | н       | н | L | Н | н | H | н | н |

| ļн             | Н              | L              | Ļ              | L              | н              | H       | н | н | L | н | н | Н | н |

| L              | L              | н              | L              | L              | н              | Н       | н | Н | н | L | Н | н | н |

| Н              | L              | н              | L              | L              | н              | н       | н | н | н | н | L | н | н |

| L              | н              | Н              | L              | L              | н              | н       | Н | н | Н | Н | Н | L | н |

| н              | н              | Н              | Ł              | L              | н              | н       | н | н | Н | Н | Н | н | L |

| ×              | Х              | Х              | L              | L              | L              | н       | Н | н | Н | H | н | Н | н |

| ×              | Х              | Х              | н              | L              | L              | н       | н | н | н | н | н | н | н |

| ×              | Х              | Х              | L              | н              | L              | н       | н | н | Н | н | н | Н | Н |

| ×              | Х              | Х              | н              | Н              | L              | н       | н | н | Н | н | н | н | н |

| ×              | Х              | Х              | н              | L              | Н              | ļн      | н | Н | н | Н | Н | н | н |

| х              | х              | Х              | L              | н              | Н              | н       | Н | H | Н | Н | н | н | Н |

| Х              | х              | Х              | н              | Н              | H              | H       | н | Н | Н | н | н | Н | Н |

#### **Applications of the 8205**

The 8205 can be used in a wide variety of applications in microcomputer systems. I/O ports can be decoded from the address bus, chip select signals can be generated to select memory devices and the type of machine state such as in 8008 systems can be derived from a simple decoding of the state lines (S0, S1, S2) of the 8008 CPU.

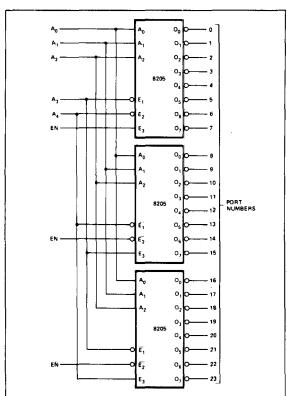

#### I/O PORT DECODER

Shown in the figure below is a typical application of the 8205. Address input lines are decoded by a group of 8205s (3). Each input has a binary weight. For example, A0 is assigned a value of 1 and is the LSB; A4 is assigned a value of 16 and is the MSB. By connecting them to the decoders as shown, an active low signal that is exclusive in nature and represents the value of the input address lines, is available at the outputs of the 8205s.

This circuit can be used to generate enable signals for I/O ports or any other decoder related application.

Note that no external gating is required to decode up to 24 exclusive devices and that a simple addition of an inverter or two will allow expansion to even larger decoder networks.

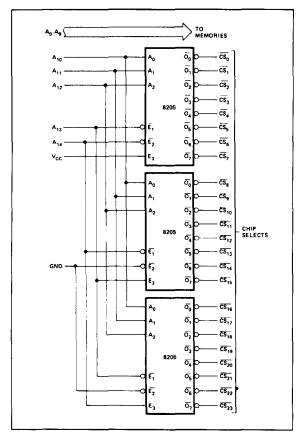

#### **CHIP SELECT DECODER**

Using a very similar circuit to the I/O port decoder, an ar-

Figure 4. I/O Port Decoder

ray of 8205s can be used to create a simple interface to a 24K memory system.

The memory devices used can be either ROM or RAM and are 1K in storage capacity. 2708s and 2114As are devices typically used for this application. This type of memory device has ten (10) address inputs and an active "low" chip select ( $\overline{CS}$ ). The lower order address bits A0–A9 which come from the microprocessor are "bussed" to all memory elements and the chip select to enable a specific device or group of devices comes from the array of 8205s. The output of the 8205 is active low so it is directly compatible with the memory components.

Basic operation is that the CPU issues an address to identify a specific memory location in which it wishes to "write" or "read" data. The most significant address bits A10-A14 are decoded by the array of 8205s and an exclusive, active low, chip select is generated that enables a specific memory device. The least significant address bits A0-A9 identify a specific location within the selected device. Thus, all addresses throughout the entire memory array are exclusive in nature and are non-redundant.

This technique can be expanded almost indefinitely to support even larger systems with the addition of a few inverters and an extra decoder (8205).

Figure 5. 24K Memory Interface

# **ABSOLUTE MAXIMUM RATINGS\***

| Temperature Under Bias:       |                   |

|-------------------------------|-------------------|

| Ceramic                       | 65°C to +125°C    |

| Plastic                       | 65°C to +75°C     |

| Storage Temperature           | 65°C to +160°C    |

| All Output or Supply Voltages | 0.5 to +7 Volts   |

| All Input Voltages            | 1.0 to +5.5 Volts |

| Output Currents               | 125 mA            |

\*NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device a reliability.

# **D.C. CHARACTERISTICS** $(T_A = 0^{\circ}C \text{ to } +75^{\circ}C, V_{CC} = 5V \pm 5\%)$

| 0)/14001        | DA DAME TED                          | LI   | MIT   | 118117 | TEST CONDITIONS                                    |  |  |

|-----------------|--------------------------------------|------|-------|--------|----------------------------------------------------|--|--|

| SYMBOL          | PARAMETER                            | MIN. | MAX.  | UNIT   |                                                    |  |  |

| I <sub>F</sub>  | INPUT LOAD CURRENT                   |      | -0.25 | - mA   | V <sub>CC</sub> = 5.25V, V <sub>F</sub> = 0.45V    |  |  |

| IR              | INPUT LEAKAGE CURRENT                |      | 10    | μA     | V <sub>CC</sub> = 5.25V, V <sub>R</sub> = 5.25V    |  |  |

| v <sub>c</sub>  | INPUT FORWARD CLAMP VOLTAGE          |      | -1.0  | V      | $V_{CC} = 4.75V, I_{C} = -5.0 \text{ mA}$          |  |  |

| V <sub>OL</sub> | OUTPUT "LOW" VOLTAGE                 |      | 0.45  | V      | V <sub>CC</sub> = 4.75V, I <sub>OL</sub> = 10.0 mA |  |  |

| V <sub>он</sub> | OUTPUT HIGH VOLTAGE                  | 2.4  |       | V      | $V_{CC} = 4.75V, I_{OH} = -1.5 \text{ mA}$         |  |  |

| V <sub>IL</sub> | INPUT "LOW" VOLTAGE                  |      | 0.85  | V      | V <sub>CC</sub> = 5.0V                             |  |  |

| V <sub>IH</sub> | INPUT "HIGH" VOLTAGE                 | 2.0  |       | V      | V <sub>CC</sub> = 5.0V                             |  |  |

| <sup>l</sup> sc | OUTPUT HIGH SHORT<br>CIRCUIT CURRENT | 40   | -120  | mA     | V <sub>CC</sub> = 5.0V, V <sub>OUT</sub> = 0V      |  |  |

| V <sub>ox</sub> | OUTPUT "LOW" VOLTAGE  @ HIGH CURRENT |      | 0.8   | ٧      | V <sub>CC</sub> = 5.0V, I <sub>OX</sub> = 40 mA    |  |  |

| l <sub>cc</sub> | POWER SUPPLY CURRENT                 |      | 70    | mA     | V <sub>CC</sub> = 5.25V                            |  |  |

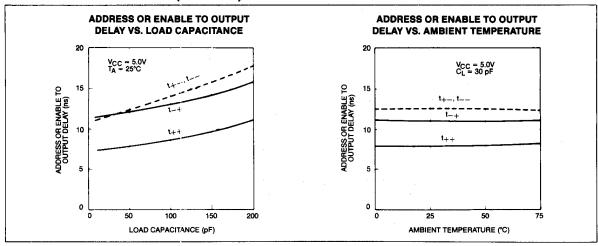

# **A.C. CHARACTERISTICS** ( $T_A = 0^{\circ}C$ to $+75^{\circ}C$ , $V_{CC} = 5V \pm 5\%$ ; unless otherwise specified)

| Symbol              | Parameter               | Max. Limit | Unit | Test Conditions                 |

|---------------------|-------------------------|------------|------|---------------------------------|

| t <sub>++</sub>     |                         | 18         | ns   |                                 |

| t_+                 | ADDRESS OR ENABLE TO    | 18         | ns   |                                 |

| t,_                 | OUTPUT DELAY            | 18         | ns   |                                 |

| t                   |                         | 18         | ns   |                                 |

| C <sub>IN</sub> (1) | INPUT CAPACITANCE P8205 | 4(typ.)    | pF   | f = 1 MHz, V <sub>CC</sub> = 0V |

| •                   | C8205                   | 5(typ.)    | ρF   | VBIAS = 2.0V, TA = 25°C         |

<sup>1.</sup> This parameter is periodically sampled and is not 100% tested

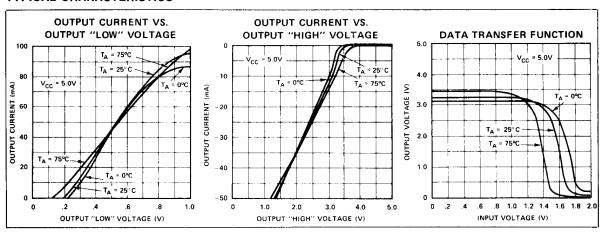

#### TYPICAL CHARACTERISTICS

6-56 AFN-00204C

# **TYPICAL CHARACTERISTICS (Continued)**

# **SWITCHING CHARACTERISTICS**

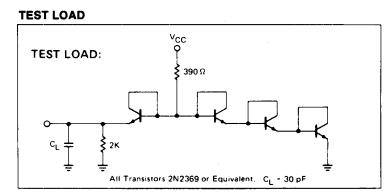

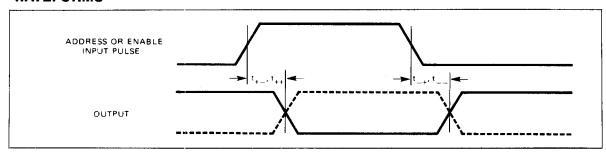

#### **CONDITIONS OF TEST:**

Input pulse amplitudes: 2.5V

Input rise and fall times: 5 nsec

between 1V and 2V

Measurements are made at 1.5V

#### **WAVEFORMS**

6-57 AFN-00204C